고정 헤더 영역

상세 컨텐츠

본문

머신비전에서 트리거 분배기만으로는 왜 부족할까? | Miss Trigger, FPGA Timing, ETIO 완전 정리

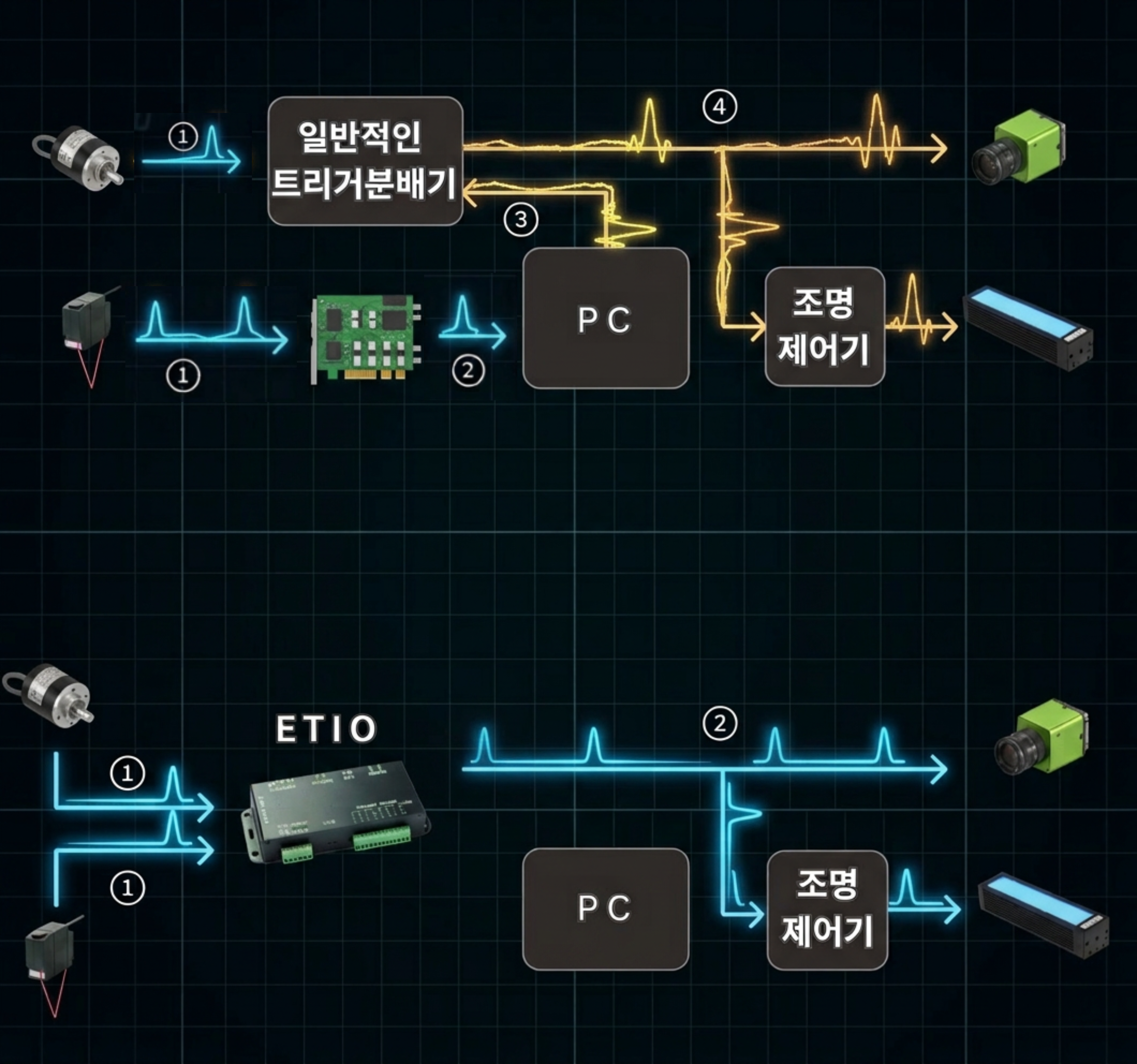

머신비전에서 트리거 분배기(Trigger Divider)란 하나의 입력 신호를 여러 장비로 나누어 전달하는 장치를 의미합니다.

하지만 고속 라인스캔(Line Scan) 검사나 엔코더 기반 정밀 동기 제어가 필요한 환경에서는 단순 분배만으로는 정확한 타이밍을 보장하기 어렵습니다. 실제 현장에서는 이 차이 때문에 Miss Trigger, 위치 오차, 검사 누락, 배선 복잡도 증가 같은 문제가 발생합니다.

핵심 요약 : 머신비전 검사 정확도는 카메라 성능만이 아니라, 언제 촬영하고 어떻게 동기화하느냐를 결정하는 타이밍 인프라에서 좌우됩니다.

머신비전에서 Miss Trigger가 발생하는 이유

고속 검사 라인을 설계하다 보면 가장 먼저 부딪히는 문제가 바로 타이밍(Timing)입니다. 카메라, 조명, 엔코더, 센서가 각각 제때 동작해야 하는데, 기존의 단순 Divider 구조는 신호를 나누는 역할에 집중되어 있어 시스템 전체의 동기화까지 책임지지 못하는 경우가 많습니다.

1. 신호 지연(Latency)

OS나 PLC를 거치면 미세한 처리 지연이 발생할 수 있습니다. 저속 장비에서는 문제가 잘 드러나지 않지만, 고속 라인스캔 검사에서는 이 미세한 지연이 촬영 위치 오차와 검사 불안정으로 이어질 수 있습니다.

2. 복잡한 배선 구조

엔코더 입력, 트리거 생성, 분배, 디지털 I/O 제어를 각각 다른 장비로 처리하면 배선이 복잡해지고 구조가 분산됩니다. 이런 구조는 설치와 유지보수를 어렵게 만들고, 현장 트러블 발생 시 원인 추적도 힘들어집니다.

3. 노이즈 취약성

산업 현장에서는 SSR, 모터, 인버터, 릴레이 등에서 발생하는 전기적 노이즈가 흔합니다. 노이즈 대응이 약한 구조에서는 오동작, 신호 깨짐, Miss Trigger가 발생하기 쉽습니다.

즉, 단순 트리거 분배만으로는 고속 머신비전 검사에 필요한 Line Scan Timing, Encoder Trigger, Camera Synchronization을 안정적으로 만들기 어렵습니다.

Pipeline Trigger가 필요한 이유

이 문제를 해결하기 위해 중요한 개념이 바로 Pipeline Trigger(파이프라인 트리거)입니다. 이는 단순히 신호를 한 번 보내는 것이 아니라, 촬영(Image Acquisition)과 처리(Processing)가 고속 라인에서도 안정적으로 이어질 수 있도록 타이밍 구조를 설계하는 방식입니다.

머신비전 시스템에서 중요한 것은 “신호를 나눴는가”가 아니라,

“카메라, 조명, 엔코더, 검사 위치가 하나의 기준 시간축에서 동작하는가”입니다.

PLC와 FPGA 타이밍 제어의 차이

PLC / OS 기반 제어

PLC 기반 시스템은 Scan Time의 영향을 받으며, OS 기반 제어는 소프트웨어 스케줄링과 처리 부하에 영향을 받을 수 있습니다. 따라서 고속 검사에서 일정한 타이밍을 유지하기 어려운 경우가 있습니다.

FPGA 기반 제어

FPGA 기반 시스템은 하드웨어 레벨에서 직접 신호를 처리하므로, 소프트웨어나 OS의 간섭 없이 보다 정밀하고 안정적인 실시간 타이밍 제어가 가능합니다. 그래서 FPGA Synchronization은 고속 머신비전 검사에서 중요한 기준이 됩니다.

ETIO란 무엇인가? | 단순 Divider를 넘어선 FPGA 타이밍 인프라

ETIO는 단순히 신호를 나눠주는 Divider가 아니라,

트리거 생성(Generation) + 체배(Multiplication) + 분배(Distribution) + 동기화(Synchronization)

를 하나로 통합한 FPGA 기반 타이밍 인프라 솔루션입니다.

기존 Divider vs ETIO 비교

ETIO의 핵심 기능 정리

1. Zero Delay 기반 초정밀 타이밍

FPGA 구조를 적용하여 OS나 PLC 간섭 없이 빠르고 안정적인 타이밍 제어가 가능합니다. 라인 속도가 빨라져도 Miss Trigger를 최소화하는 데 유리합니다.

2. Encoder Trigger 생성 및 체배 지원

엔코더 입력 신호를 기반으로 위치 트리거를 생성하고, 4배 / 16배 / 32배 체배 기능을 지원합니다. 예를 들어 1kHz 입력 시 최대 32kHz 수준의 트리거 출력 구성이 가능해 고속 검사 환경에 적합합니다.

3. Working Area 기능

특정 위치 구간에서만 트리거를 발생시키는 기능으로, 불필요한 촬영과 데이터 처리를 줄이는 데 도움이 됩니다. 이는 검사 효율과 시스템 최적화 측면에서 매우 중요합니다.

4. Isolated I/O와 디지털 노이즈 필터

노이즈가 심한 공정에서도 안정성을 높이기 위해 Isolated I/O 구조와 디지털 노이즈 필터를 적용할 수 있습니다. 이는 반도체, 2차전지, 자동차 부품 검사처럼 전기적 간섭이 많은 현장에서 특히 중요합니다.

ETIO가 필요한 적용 분야

- 2차전지 검사 : 고속 라인스캔, 위치 기반 트리거, 다면 검사 동기화

- 반도체 검사 : Miss Trigger 최소화, 안정적 타이밍 확보, 노이즈 대응

- 디스플레이 검사 : 넓은 영역의 고속 촬영과 정밀한 Timing Control

- 자동차 부품 검사 : 엔코더 기반 정밀 위치 동기 제어

- 다면 검사 시스템 : 전면 / 측면 / 후면 카메라와 조명을 동시에 맞춰야 하는 구조

결론 | 머신비전 검사 정확도는 타이밍 인프라에서 결정된다

결론적으로, 머신비전 검사 정확도는 카메라 스펙만으로 결정되지 않습니다.

트리거 생성, 엔코더 기반 위치 제어, 조명과 카메라의 동기화, 노이즈 대응을

하나의 구조로 설계해야 고속 라인에서도 안정적인 검사가 가능합니다.

단순 Divider는 신호 분배에는 적합할 수 있지만,

고속 검사에서는 FPGA 기반 통합 타이밍 솔루션이 더 중요한 기준이 됩니다.

시스템 전체의 타이밍 인프라를 고민한다면, ETIO는 그 해답이 될 수 있습니다.

머신비전 트리거, Trigger Divider, Miss Trigger, Pipeline Trigger, Encoder Trigger, FPGA Synchronization, Line Scan Timing, 머신비전 동기화, 고속 검사 타이밍, ETIO

Pipeline Trigger / Machine Vision / FPGA Architecture

'제품 기술 이야기 > 기초 원리' 카테고리의 다른 글

| 복잡한 트리거 해결부터 검증까지 (0) | 2026.03.24 |

|---|---|

| 파이프라인 트리거 (병렬구조 트리거 방식) (0) | 2026.03.24 |

| 트리거 분배기란? (0) | 2026.03.23 |

| 머신비전 기초정리 [전체 보기] (0) | 2026.03.20 |

| 머신비전 렌즈 종류 완전 정리 (0) | 2026.03.20 |