고정 헤더 영역

상세 컨텐츠

본문

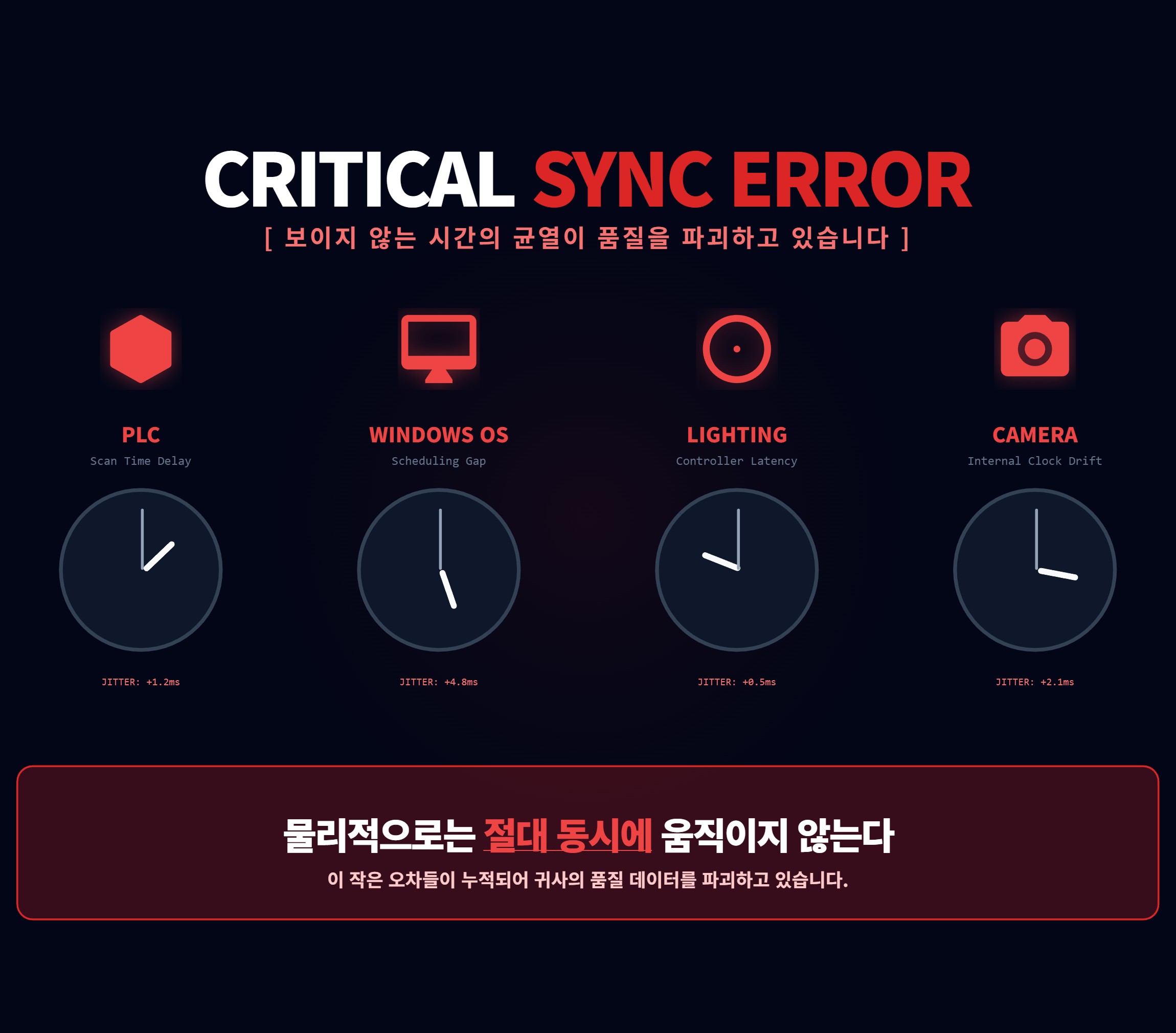

머신비전이 ‘동시에’ 움직이지 않는 이유

범인은 영상 처리 이전의 ‘시간의 정렬 상태’입니다.

머신비전 현장에서 가장 엔지니어를 괴롭히는 순간은 “분명 어제까지는 멀쩡하던 장비가 오늘 갑자기 오검사를 쏟아낼 때”입니다.

카메라를 닦고 조명을 조정해 봐도 문제는 해결되지 않습니다.

성원기술 기술백서 제2강에서는 영상 처리 이전의 보이지 않는 영역,

바로 ‘시간의 정렬 상태’를 다룹니다.

1. 머신비전 시스템은 사실 ‘각자’ 움직이고 있습니다

많은 현장에서 머신비전 시스템은 다음과 같은 구조로 신호를 주고받습니다.

- PLC에서 트리거(촬영 신호) 생성

- 조명 컨트롤러에서 스트로브 제어

- 카메라 내부 타이밍으로 셔터 동작

- 엔코더 신호 소프트웨어 처리

각 장비는 자기 시계 기준으로는 정확히 동작합니다.

하지만 문제는 각자의 ‘시간 기준’이 다르다는 점입니다.

PLC의 스캔 타임, Windows OS의 연산 시간, 조명 컨트롤러의 내부 클럭은

서로 연결되어 있는 것 같지만 물리적으로는 완전히 따로 움직입니다.

2. “어제는 정상, 오늘은 불량” – 범인은 ‘시간의 정렬’

장비 사양도, 환경도 그대로인데 갑자기 오검사가 발생하는 이유는 장비 노후화 때문이 아닙니다.

바로 ‘시간의 정렬 상태’가 미세하게 흔들렸기 때문입니다.

- PLC 스캔 타임의 미세한 변화

- OS 스케줄링(멀티태스킹)에 의한 지연

- 통신 데이터 누적에 따른 지연

이러한 요소들이 겹치면서 트리거 → 조명 → 셔터로 이어지는 순서가 매번 미세하게 달라집니다.

영상만 보면 “이미지가 이상하게 어둡거나 흔들린다”고 느껴지지만, 실제로는 신호들이 찰나의 순간에 서로 어긋나고 있는 것입니다.

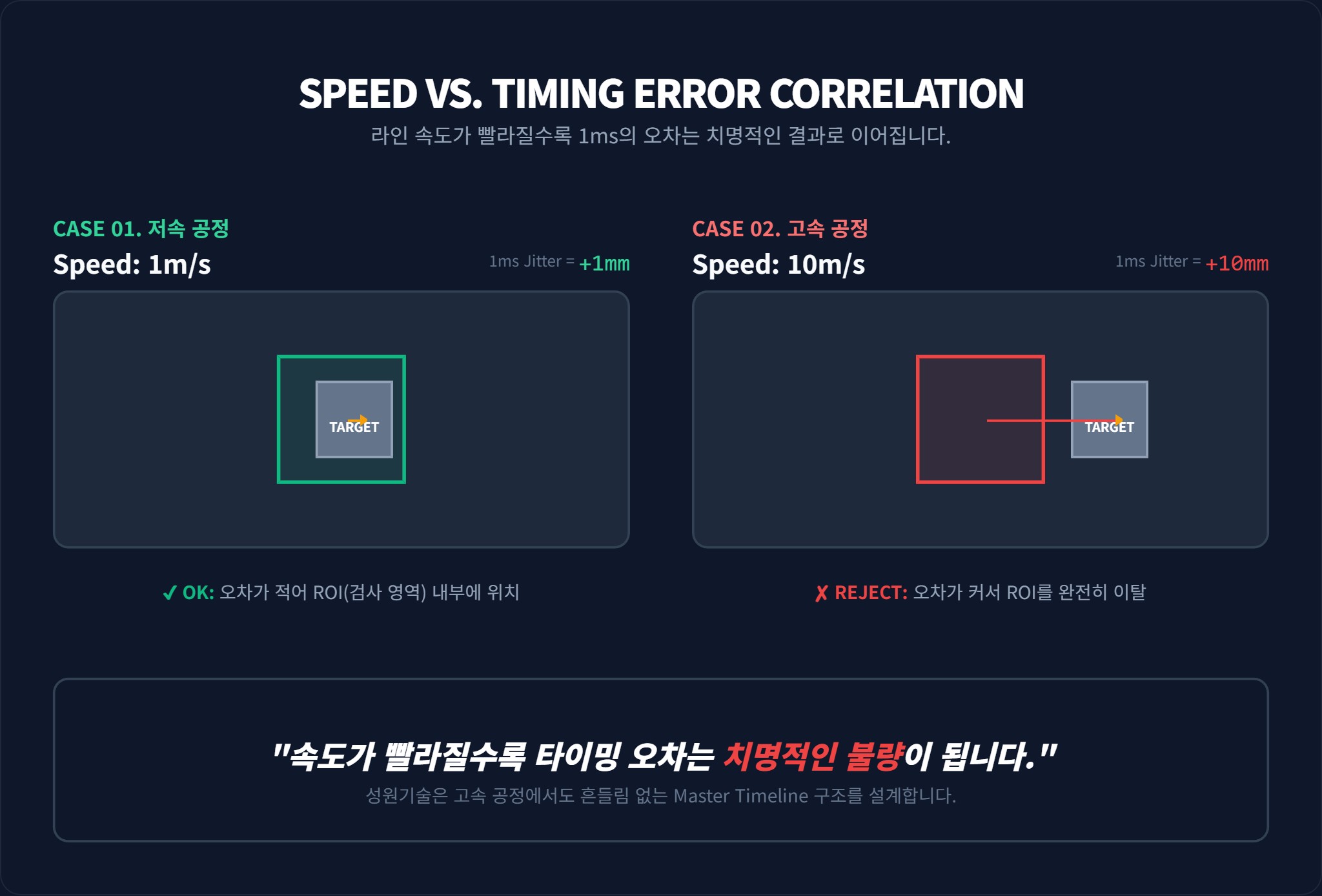

3. 고속 라인일수록 ‘0.001초’는 거대한 벽이 됩니다

저속 라인에서는 1ms(0.001초)의 지연이 큰 문제가 되지 않을 수 있습니다.

하지만 고속 라인으로 넘어가면 이야기는 완전히 달라집니다.

V = d / t 공식에 따라 속도(V)가 빨라질수록

허용 가능한 시간 오차(t)는 급격히 줄어듭니다.

에지 검출 실패, AI 판독 불안정 등은 속도 때문이 아니라,

속도가 빨라지면서 숨겨져 있던 ‘구조적 시간 오차’가 드러난 결과입니다.

- V (Velocity): 컨베이어 벨트나 설비의 주행 속도

- d (Distance): 지터(Jitter)로 인해 발생하는 위치 오차(거리)

- t (Time): 신호 지연/흔들림으로 발생하는 시간 오차(지터)

4. 왜 ‘설정 튜닝’은 임시방편일 뿐인가요?

문제가 생기면 흔히 트리거 딜레이를 조정하거나 조명 시간을 재설정하는 ‘튜닝’을 합니다.

하지만 이는 깨진 항아리에 테이프를 붙이는 것과 같습니다.

환경이나 속도, 부하 조건이 조금만 바뀌어도 튜닝값은 다시 무용지물이 됩니다.

결국 재현성도, 표준화도 확보할 수 없는 악순환에 빠지게 됩니다.

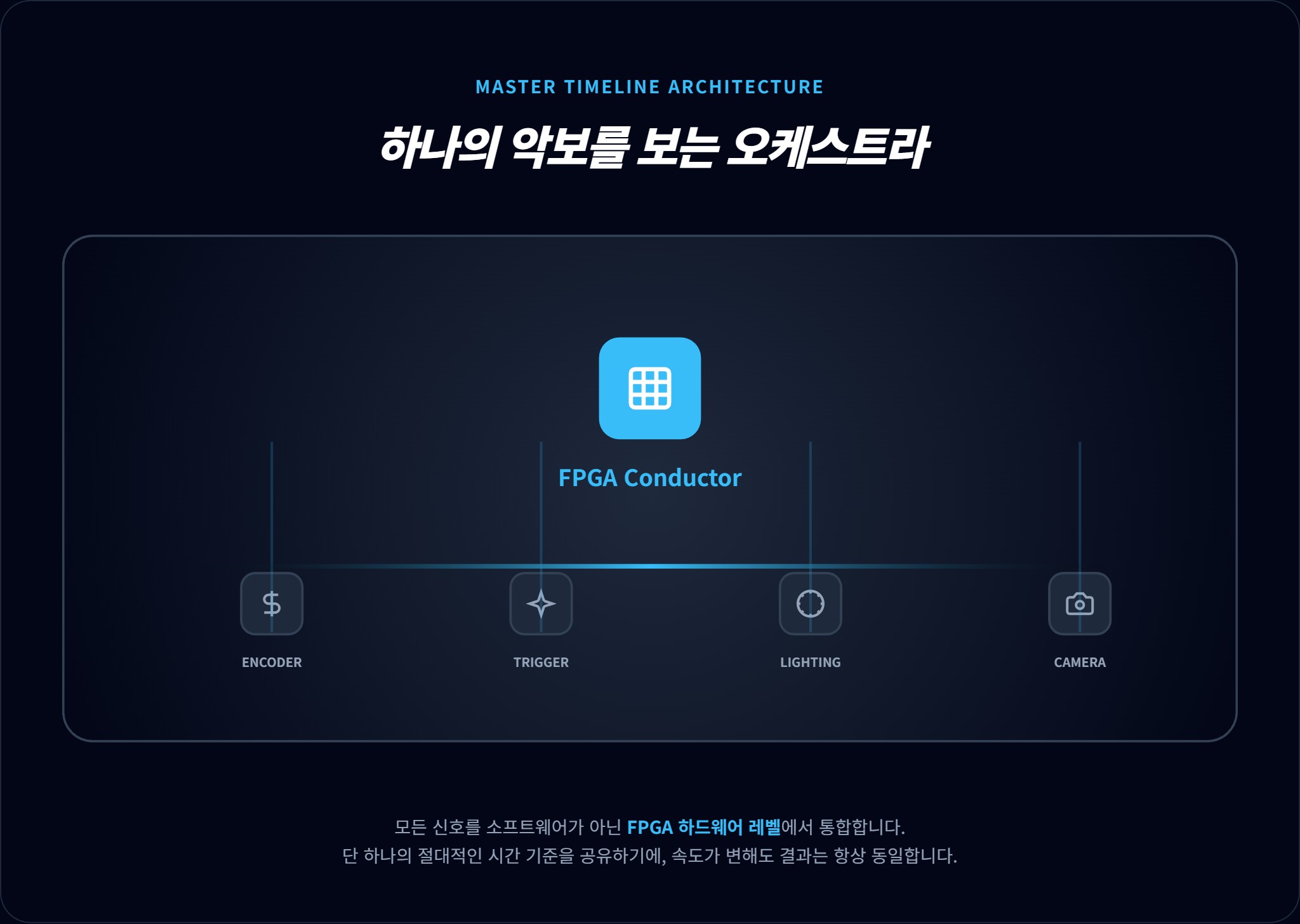

5. 해답은 ‘단일 시간축(Master Timeline)’ 구조입니다

성원기술은 “어떻게 보정할 것인가?”를 고민하지 않습니다.

대신 “애초에 왜 어긋나게 두는가?”라고 묻습니다.

소프트웨어나 PLC 스캔 타임에 의존하지 않고,

FPGA 하드웨어 레벨에서 단 하나의 시간 기준으로 모든 신호를 통합하는 것.

이것이 바로 성원기술의 Master Timeline Architecture입니다.

속도가 바뀌어도, 장비가 바뀌어도

항상 같은 타이밍, 같은 결과를 약속합니다.

성원기술(SeongWon Technology)

#머신비전 #성원기술 #기술백서 #스마트공장 #FPGA #동기화 #지터 #품질관리 #제조혁신

'제품 기술 이야기 > 장비 설계' 카테고리의 다른 글

| [기술백서-장비편] 5강 PoC에서 반드시 검증해야 할 것들 (0) | 2026.01.05 |

|---|---|

| [기술백서 장비편] 4강 PLC · WindowOS · FPGA 구조의 본질적 차이 (0) | 2026.01.02 |

| [기술백서 장비편] 3강 신호 가시화와 설명 가능한 품질의 시작 (0) | 2026.01.02 |

| [기술백서-장비편] 1강 검사의 품질 향상 방법 (0) | 2026.01.02 |

| ETIO-2444 기능 그림으로 한 눈에 보기 (0) | 2025.12.03 |